Models of Clustered Photolithography Tools for Fab-Level Simulation: From Affine to Flow Line

Abstract

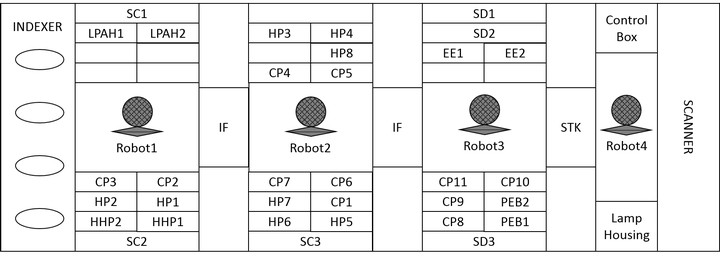

Fab-level discrete-event simulation is an important practical tool for the analysis and optimization of semiconductor wafer fabricators. In such facilities, a clustered photolithography tool (CPT) is by far the most expensive tool and often the capacity bottleneck. In this paper, we consider linear, affine, flow line, and detailed models of CPTs for use in fab-level simulation. We develop extensions to affine and flow line models and demonstrate exactly how to convert raw CPT data into the various models. Using a detailed CPT model based on industry data as the baseline, numerical experiments are conducted to test the models’ fidelity for cycle time, lot residency time, and throughput. We also compare the computational burden of each model class. Further simulations are conducted to test the models’ robustness to changing fab conditions, e.g., when lot size or train size changes. Flow line models are shown to be more accurate and robust than linear or affine models and require approximately 200 times less computation than detailed models.